Manufactura De Semiconductores 6p5b4t

This document was ed by and they confirmed that they have the permission to share it. If you are author or own the copyright of this book, please report to us by using this report form. Report 2z6p3t

Overview 5o1f4z

& View Manufactura De Semiconductores as PDF for free.

More details 6z3438

- Words: 16,798

- Pages: 67

Semiconductores: Qué son y cómo se fabrican? Posted on by mario

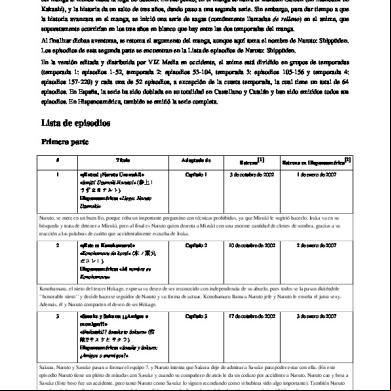

Object 1

De todos los materiales electrónicos, quizás el que mayor revolución ha causado en el mundo de la electrónica son los semiconductores. Gracias a tecnología de semiconductores la electrónica ha podido pasar de aplicaciones militares y científicas de alto nivel hasta aplicaciones caseras comunes y de bajo costo. En la actualidad la mayor parte de nuestra vida gira alrededor de materiales semiconductores. Los equipos de radio que utilizamos para comunicarnos, los sistemas de ignición e inyección de los automóviles modernos, las computadoras que usamos a diario todos son dependientes de estos singulares materiales. Un semiconductor es un material que bajo ciertas condiciones resulta ser aislante, pero bajo otras condiciones resulta ser conductor, de ahí su nombre. Por lo general, los semiconductores son aislantes, pero conforme aumenta su temperatura se vuelven conductores. Cómo se fabrica un semiconductor? Un semiconductor se fabrica mediante un proceso que se conoce como dopado. El dopado consiste en introducir impurezas dentro de cristales de un material base durante su formación. Los materiales más comunes utilizados como bases son el Germanio (Ge) y el Silicio (Si). En las plantas productoras de semiconductores, se inicia un crecimiento de cristales de Germanio, y mientras éstos crecen son expuestos a dosis controladas de Arsénico (As). El Arsénico se introduce en los cristales y les provoca un efecto de carga eléctrica: como el átomo de Arsénico posee cinco electrones y el de germanio solo cuatro, existe una carga resultante negativa en el cristal. El material resultante se conoce como Germanio N (N=negativo).

En el caso del Silicio, se puede utilizar Fósforo (P), para producir un efecto similar que da como resultado el Silicio N. Si en vez de crear una carga negativa se quiere crear una carga positiva, el material se expone a Galio (Ga) en el caso del Germanio, o a Boro (B) en el caso del Silicio. Esto produce Germanio P y Silicio P. La diferencia fundamental en estos materiales dopados es que poseen una carga eléctrica positiva o negativa. Como vimos en el capítulo de electricidad, la materia en su estado normal es eléctricamente neutra (posee carga cero). Esta carga que se les da nos permite lograr efectos eléctricos bastante interesante y útiles.

manufactura de semiconductores https://www.electronicosonline.com/kla-tencor-lanza-sistema-metrologico-para-ics-de-10-nm/

KLA Tencor lanza sistema metrológico para ICs de 10 nm marzo 21, 2017 Medición y Pruebas

• • •

Facebook Twitter Google + El área de calidad de las compañías manufactureras de circuitos ahora cuentan con una nueva herramienta para realizar las mediciones en arquitecturas menores a 10 nanómetros. (ElectronicosOnline.com Magazine / Oswaldo Barajas) La manufactura de circuitos electrónicos con arquitecturas inferiores a 10 nanómetros, además de requerir de técnicas de fabricación especiales, también necesitan un control exclusivo por parte del personal de calidad y medición.

Cualquier tolerancia que se encuentre fuera del rango permitido puede causar severos problemas en el ciclo de producción, y en caso de llegar a la fase final del proceso, el producto puede salir con fallas técnicas. A medida que las arquitecturas se miniaturizan más y más, los ingenieros de calidad y metrología están sometidos a mayor estrés para llevar a cabo su trabajo con el menor índice de errores, pero no solo se basan en sus conocimientos académicos y habilidades personales, también requieren de instrumental adecuado para evitar que se filtren piezas con errores. Para la mayoría de las empresas manufactureras la oferta de herramientas no es lo suficientemente vasta para cubrir sus necesidades en áreas de calidad, no obstante, compañías como KLA Tencor han comenzado a desarrollar soluciones para el área de medición y pruebas.

Los nuevos instrumentos de metrología de KLA Tencor están orientados a la manufactura de circuitos integrados con arquitecturas menores de 10 nanómetros.

El más reciente producto de KLA es un sistema de metrología denominado KLA Archer 600, que presuntamente auxilia a las compañías a fabricar grandes volúmenes de componentes con dimensiones menores a 10 nanómetros y sin imperfecciones. Pero no solo el Archer 600 forma parte del portafolio de soluciones de KLA para el sector de manufactura electrónica, también otros instrumentos metrológicos como el WaferSight PWG2, también está orientado a realizar mediciones en función con patrones geométricos de las obleas; el SpectraShape 10K para sistemas ópticos, y finalmente el SensArray HighTemp, para mediciones micrométricas ‘in-situ’. De acuerdo a la compañía, estos equipos de metrología tienen la capacidad de trabajar con las más recientes técnicas de manufactura electrónica incluyendo SAQP (Self-Aligned Quadruple Patterning) y litografía extrema por ultravioleta (EUV).

- PUBLICIDAD -

Object 2

“Los fabricantes de dispositivos de última generación enfrentan retos con geometrías extremadamente pequeñas”, manifestó Oreste Donzella, Director de Marketing de KLA Tencor. “Para

comprender los errores de geometrías, los fabricantes de chips requieren cuantificar las variaciones de los procesos, aislar sus fuentes y fijar los problemas detectados. Los nuevos sistemas de metrología anunciados hoy generan información crítica para que los ingenieros pueden utilizarla en la especificación de correcciones detalladas en escaneo de módulos de litografía y aplicativo al mejoramiento de procesos de grabado, películas especiales y otros componentes. Nuestras nuevas geometrías de obleas, con sistemas modelados de dimensiones ópticas críticas y sistemas de medición térmica ‘in-situ’, juegan un papel importante para alcanzar un buen desempeño de multipatrón y mejora los resultados de litografía EUV”, puntualizó. Por ejemplo, el Archer 600 amplía la tecnología de metrología de superposición basada en imágenes con nuevas ópticas y nuevos objetivos de medición, los cuales permiten a los fabricantes detectar errores menores a 3 nanómetros para dispositivos lógicos avanzados como las nuevas memorias Flash. En el caso de la herramienta ProAIM ofrece una mejor resiliencia a las variaciones de los procesos y entrega una correlación entre los errores de superposición entre los objetivos y los dispositivos, generando una mayor precisión durante las mediciones.

La compañía cuenta con un portafolio de diferentes equipos especializados para la industria de manufactura electrónica.

Entre las características técnicas asociadas a las nuevas plataformas de la compañía, destacan funciones adicionales como una configuración de brillo y enfoque. Además de la adición de módulos de polarización para garantizar una mejor retroalimentación en la detección de errores y el control de análisis sobre diferentes tipos de materiales y capas. La firma subrayó que sus nuevos equipos también fueron desarrollados para fabricantes de dispositivos FinFET y memorias NAND, que son trabajadas con materiales de Silicio-Germanio (SiGe) o CD. Para mayor información sobre detalles y aplicaciones técnicas de estas nuevas soluciones Tencor, puede acceder al sitio Web de la compañía haciendo clic en el siguiente enlace.

https://www.electronicosonline.com/china-respondera-a-eeuu-con-industria-de-semiconductores-masfuerte/

China responderá a EEUU con industria de semiconductores más fuerte enero 31, 2017 Industria y Negocios

• • •

Facebook Twitter Google + Gobierno, líderes industriales e inversionistas chinos, anunciaron que invertirán 160 mil millones de dólares para fortalecer su industria, a dos semanas después de que la Casa Blanca anunciara planes para combatir lo que llamaron “prácticas injustas” de algunos países en la industria. (ElectronicosOnline.com Magazine / Oswaldo Barajas) La llegada del magnate Donald Trump a la Casa Blanca, ha dejado a socios tradicionalmente comerciales de Estados Unidos en un estado de incomodidad y decepción, al grado que las relaciones diplomáticas se han visto afectadas principalmente con países que por décadas han sido sus aliados comerciales en áreas de proveeduría de insumos y manufactura, como China, país que ha decidido responder al nuevo presidente norteamericano con una nueva campaña para reforzar su gran industria de semiconductores.

La conmoción del gobierno chino se debe a que Trump ha señalado a este país asiático, además de otros países latinoamericanos, como los causantes del desempleo en Estados Unidos, aseverando que las compañías estadounidenses han desviado las oportunidades de los ciudadanos norteamericanos al invertir y expandirse en otras regiones fuera del país, incluyendo industrias clave como automotriz y electrónica. En el caso específico de la industria de semiconductores, la situación se ha vuelto más hostil debido a un reporte difundido por funcionarios del Consejo de Asesores en Ciencia y Tecnología (PCAST) de la Casa Blanca a principios de enero, en el que convocaron a una acción internacional en contra de lo que ellos mismos definieron como “prácticas injustas” de algunos países que dominan el mercado de dispositivos semiconductores, componentes medulares de la electrónica moderna.

Las compañías planean comenzar a manufacturar circuitos de 14 nanómetros con esta fuerte inversión.

El informe enérgico de la Casa Blanca fue promovido directamente por los representantes de la industria norteamericana de semiconductores, quienes consideraron que la ambición agresiva de China por convertirse en un actor global en el mercado de chips, traerá serios problemas a las compañías americanas, por lo que solicitaron la intervención de los altos mandos del gobierno norteamericano para crear una estructura que permita proteger a las firmas domésticas y serenar las intenciones comerciales de China en este importante mercado. “PDCAST encontró que la industria de semiconductores de Estados Unidos enfrenta mayores retos con una amplia gama de implicaciones para la economía y la seguridad nacional. La innovación ya se está desacelerando, ya que la industria de semiconductores se enfrenta a limitantes tecnológicos fundamentales en mercados de rápida evolución. Ahora, una impulsiva iniciativa de China para remodelar el mercado a favor de sus intereses, amenaza la competitividad de la industria norteamericana y los beneficios nacionales e internacionales que ofrece la industria estadounidense”, comenta el reporte elaborado por los funcionarios del PDCAST. Esta posición no fue bien recibida por el gobierno de China quien de inmediato respondió con un anuncio que involucra la inversión de 160 mil millones de dólares para fortalecer y detonar su industria nacional de semiconductores para consolidar su posicionamiento como el país más importante en el suministro, manufactura y diseño de materias primas para la industria electrónica global.

Comparativa de exportaciones e importaciones de ICs por parte de China.

De acuerdo al diario Bloomberg, el gobierno de Xi Jinping, considerado el gran líder del Partido Comunista, se ha propuesto impulsar su brazo doméstico de tecnología para independizarse de las industrias proveedoras extranjeras. La compaña del gobierno chino ha comenzado con una agresiva difusión y convocatoria a nivel nacional para invitar a las compañías chinas y los medios de prensa para dar a conocer que los 160 mil mdd se invertirán en los siguientes 10 años para conferir las capacidades e infraestructura necesarias a la industria china para desarrollar sus propios chips, lo que será tanto como las inyecciones de capital que el fabricante norteamericano Intel Corporation, ha gastado en la última década para construir fábricas y mantener su ritmo de Investigación y Desarrollo (I+D), colocándola como el fabricante de chips más importante del mundo.

Xi Jinping, considerado el gran líder del Partido Comunista.

Cabe mencionar que al autodefinirse China como un país dependiente de la industria extranjera, se refiere a que su industria consume más de la mitad de los semiconductores que se comercializan globalmente cada año, y sus necesidades van en aumento. Con todo y su potencial comercial, ninguna de las compañías chinas que manufacturan localmente circuitos integrados ha logrado posicionarse en el top-10 de los fabricantes de chips más importantes del mundo, ranking que encabezan las firmas norteamericanas y coreanas. Otra de las razones por la que China ha decidido tirar la casa por la ventana a favor de su industria electrónica, es porque ha gastado más dinero en importar chips de otros países que lo que ha invertido en comprar petróleo, de acuerdo a la firma de investigación Sanford C. Bernstein, citada por Bloomberg.

Compañías chinas de semiconductores que ya han comenzado a sumarse a la iniciativa del gobierno.

A esta iniciativa se han sumado directivos de fabricantes de chips como Shangai Huali Microelectronics, Advanced Micro-Fabrication Equipment (AMEC) consideradas como dos pilares en la industria china de semiconductores. China también se ha convertido en un mercado altamente lucrativo para las compañías norteamericanas, ya que el país asiático es por más el principal consumidor de insumos para la manufactura de dispositivos electrónicos, sobresaliendo chips, sensores, antenas y cámaras, por mencionar algunos para maquilar los millones de aparatos electrónicos que exporta al extranjero. Esta necesidad de componentes tiene a China con un déficit de semiconductores alto y representa para el mercado global el cliente más grande con el 45% del total de las ventas, y del total de la producción mundial de semiconductores, las compañías chinas solo participan con un 13%. Overseas gear vendors lead local ones in China; percentages indicate China market share. (Images: AMEC) Click here for larger image

https://www.electronicosonline.com/ibm-revela-primer-nodo-construido-en-7-nm/

IBM revela primer nodo construido en 7 nm noviembre 17, 2015 Diseño Analógico

• • •

Facebook Twitter Google + La compañía arrancará las pruebas técnicas para manufacturar los primeros chips desarrollados en arquitectura de 7 nanómetros. (ElectronicosOnline.com Magazine / Oswaldo Barajas)

IBM se ha adjudicado un importante avance hacia la miniaturización de los dispositivos semiconductores, después de presentado el primer nodo construido con tecnología de 7 nanómetros (nm), una dimensión equivalente a 100 mil veces más delgado que el grosor de un cabello humano.

En el reporte de prensa generado por la compañía, se indica que el grupo de ingeniería de IBM colaboró estrechamente con investigadores del Colegio de Ciencia de Nanoescala e Ingeniería del Instituto Politécnico de SUNY, en Nueva York, Estados Unidos, y en conjunto realizan las fases de prueba y validación de la estructura conformada por diminutos transistores. El documento señala que este nodo es el primero a nivel industrial en contar con este tamaño y comprobar funcionalidad operativa, ya que la tecnología de 7nm ha sido uno de los grandes retos de la industria electrónica mundial, siguiéndola como objetivo compañías clave como AMD o Intel Corporation, ARM, fabricantes de microprocesadores. Entre las grandes barreras que han impedido que la industria logre materializar dispositivos sobre 7 nanómetros, se encuentran los efectos colaterales que involucra la reducción de las arquitecturas manufacturadas con procesos convencionales, lo que genera la degradación del sistema y promueve un mayor consumo de energía, ya que al ser mucho mayor la densidad de los transistores en un trozo de Silicio más pequeño, demanda mayor control en su ciclo de desarrollo, o lo que es lo mismo la creación de nuevos procesos de manufactura.

Los investigadores que participaron en el proyecto muestran la oblea donde quedó plasmado el primer nodo construido con tecnología a 7 nanómetros

En el actual 2015, los más modernos microprocesadores están construidos sobre arquitecturas de 22nm y 14nm, aunque compañías como Intel y ARM, han anunciado que ya preparan la liberación de

tecnología de 10 nanómetros, todas estas trabajadas con procesos de manufactura convencional que no han requerido ser radicalmente modificados. Pero en este proyecto se tuvo que estructurar una técnica nueva para crear procesos de manufactura especial que permitieron la materialización del prototipo.

- PUBLICIDAD -

Object 3

Este trabajo se llevó a cabo en las instalaciones de IBM Research y presumiblemente se requirió un número considerable de innovaciones, incluyendo la integración multinivel de Silicio-Germanio (SiGe) para construir los canales de transistores y litografía de rayos ultravioleta extremos (EUV, por sus siglas en inglés), por mencionar algunos.

IBM Research colaboró con Samsung Electronics y Global Foundries para dar este importante salto en la miniaturización de chips

Al integrar estos recursos en un solo proceso industrial, los científicos estuvieron cerca de alcanzar casi el 50% de las mejoras de escalamiento tecnológico que registra la más moderna arquitectura de microprocesadores, que es de 10 nanómetros y la cual está siendo trabajada en los laboratorios de diversas compañías. De acuerdo a IBM, entre los beneficios de la nueva generación de semiconductores construidos con tecnología de 7 nanómetros, se encuentran un 50% más eficiencia energética y mayor desempeño para el procesamiento de datos, y debido a sus nuevas características, estiman que soportarán desahogadamente los requerimientos de sistemas en ‘Big Data’ y de conectividad en la Nube de Computación.

En este proyecto fue de capital importancia la participación de las compañías Global Foundries y Samsung Electronics, quienes cedieron parcialmente equipo especializado a IBM para levar a cabo el proyecto, además del Instituto Politécnico de SUNY de Nueva York, que en conjunto representan una inversión colectiva de aproximadamente 3 mil millones de dólares a un plazo de 5 años para trabajos de investigación y desarrollo dirigidos a tecnología de semiconductores en escala de 7 nm.

La industria continúa trabajando en la miniaturización de los circuitos electrónicos

“La cuestión no es si introduciremos la tecnología de 7 nanómetros a la manufactura, sino cómo, cuándo y a qué costo”, comentó John Kelly, vicepresidente de IBM Research. “Los ingenieros y científicos de IBM, así como nuestros socios, están comprometidos en este reto y están trabajando ya en la ciencia de los materiales e ingeniería de dispositivos requeridos para alcanzar las demandas de los sistemas emergentes para la Nube, ‘Big Data’, y sistemas cognitivos. Esta nueva inversión asegurará que produzcamos las innovaciones necesarias para responder a esos retos”, puntualizó. Este importante paso por parte de IBM hacia la nueva era de circuitos integrados más potentes, no ha sido la única gran aportación que ha hecho la compañía a lo largo de su historia, ya que según refiere la información de su portal, otras invenciones han sido producidas en sus laboratorios, tales como la implementación de la primera célula DRAM, las Leyes de Escalamiento Dennard o escalamiento MOSFET, foto-resistencias químicamente amplificadas, interconexión de cobre, Silicio sobre Aislante, microprocesamiento multi núcleo, litografía de inmersión, SiGe de alta velocidad, puertas dieléctricas de Alto-k, DRAM embebidas, estructura para chips 3D y aisladores de brecha aérea, por mencionar algunos. El siguiente paso por parte de IBM será someter a pruebas rigurosas la viabilidad de la tecnología para encontrar si es posible abrir terreno para su despliegue comercial.

https://www.electronicosonline.com/casas-de-diseno-chinas-se-vuelcan-por-tsmc/

Casas de diseño chinas se vuelcan por TSMC septiembre 1, 2014 Diseño Analógico, Industria y Negocios

• • •

Facebook Twitter Google +

Las nuevas arquitecturas en 28 nm para chips diversos han obligado a las casas de diseño de China a solicitar al fundidor taiwanés les manufacture sus obleas, abandonando a sus proveedores chinos por presunta obsolescencia en sus procesos. (ElectronicosOnline.com Magazine / Oswaldo Barajas) La tecnología de 28 nanómetros o menos para los más recientes circuitos integrados ha sobrepasado las capacidades de las casas de diseño chinas, quienes poco a poco comienzan a abandonar a sus proveedores de manufactura local y solicitado la ayuda a TSMC, el fundidor taiwanés más grande de semiconductores de la industria.

La razón de este éxodo comercial hacia TSMC por parte de las pequeñas empresas dedicadas al diseño electrónico o de servicios con sede en China, es que las principales fundidoras de obleas del dragón comercial se han quedado estancadas en relación con los nuevos requerimientos microelectrónicos a escala de 28 nm o menos, formato casi obligatorio para la fabricación de chips móviles y otros equipos de comunicación, informó en un comunicado la agencia de noticias Digitimes. De acuerdo al reporte, además de la obsolescencia tecnológica de muchas fundidoras chinas o también llamadas “foundries” de semiconductores, también se une a esta situación la creciente competencia entre manufactureros de electrónica local que han inyectado mayor presión a la cadena de suministro.

Las casas de diseño electrónico de China mayormente se enfocan en el diseño de procesadores para dispositivos móviles.

Entre las casas de diseño que optaron por Taiwan Semiconductor Manufacturing Company, se encuentran firmas importantes como HiSilicon Technologies, Spreadtrum Communications, Rockchip Electronics, Allwinner Technology, RDA Microelectronics y Datang, todas ellas con un grado alto de participación en el sector de tecnologías móviles del mercado chino, específicamente para el desarrollo de procesadores para smartphones, tabletas y otros equipos de comunicación.

- PUBLICIDAD -

Object 4

Por su parte, las fundidoras que han sido señaladas como principales proveedores de servicios a nivel oblea y con las cuales muchas de las empresas como las anteriormente citadas establecían relación industrial son Semiconductor Manufacturing International Corporation (SMIC) y Hejian Technology, debido a sus bajos costos de manufactura para el mercado doméstico son aún son reconocidas como entidades competentes en la región, según apunta el documento de Digitimes. Pero han observado que las exigencias de los nuevos protocolos de comunicación, incluyendo el hardware inherente a estas plataformas, han orillado a los fabricantes minoritarios de dispositivos electrónicos a optar por procesos de manufactura más avanzados como la tecnología FinFET de TSMC, en la que han visto al parecer más capacidades para que sus chips sean fabricados acorde a los requerimientos de la industria para sectores como smartphones 4G, aparatos IoT, equipo de telecomunicaciones y otras clases de gadgets con conectividad.

De acuerdo a IBS, los costos de manufactura de obleas por nodo resulta más costoso con tecnología FinFET, principal técnica utilizada por TSMC, aun así, sus servicios son más demandados.

Como resultado de este movimiento industrial, se estima que sin tomar en cuenta las órdenes de obleas generadas por MediaTek a TSMC, el total de órdenes de obleas que han estado enviando las casas de diseño chinas a la firma taiwanesa, han superado ya las registradas por las casas de diseño de Taiwán hacia TSMC.

Diversas casas de diseño de circuitos en China han comenzado a abandonar sus proveedores de fundición para solicitar a TSMC sus servicios.

Cabe mencionar que recientemente el fabricante de chips para celulares Qualcomm Inc., firmó un convenio de colaboración con SMIC, el foundry que ha visto la deserción de clientes locales, con lo cual balanceará sus pérdidas con un gigante como esta compañía que controla gran parte del suministro de chips para dispositivos móviles con su gama de microprocesadores Snapdragon. No obstante, los avances en materia de procesos de manufactura FinFET que ha promovido TSMC ha ganado terreno incluso a otros fundidores como Intel Corporation y sus técnicas de manufactura CMOS, haciendo que la firma taiwanesa se posicione como un foundry de gran poder en la industria electrónica moderna.

https://www.electronicosonline.com/tsmc-arrebata-clientes-a-intel-y-samsung/

TSMC arrebata clientes a Intel y Samsung mayo 13, 2014 Industria y Negocios

• • •

Facebook Twitter Google + El fabricante de circuitos electrónicos más importante TSMC continúa apoderándose del mercado, consiguiendo la confianza de clientes de Intel y Samsung. (ElectronicosOnline.com Magazine / Oswaldo Barajas) La compañía taiwanesa de manufactura de circuitos integrados TSMC, manufacturará chips a Altera y Apple, quienes fueran clientes de Intel y Samsung, respectivamente, logrando de esta forma un posicionamiento sólido en la industria electrónica global.

Taiwan Semiconductor Manufacturing Corp., es la firma fundidora o “foundry” de circuitos y compite directamente con otras compañías ‘foundries’ como Intel Corporation y Samsung Electronics, las cuales también ofrecen su infraestructura fabril a otras empresas para fabricarles sus productos. Debido a que no todas las empresas tienen capacidad industrial de fabricación en masa o como se conoce esta modalidad en inglés “fabless”, solamente se limitan a diseñar sus chips y posteriormente con prototipo en mano, buscan a un ‘foundry’ que les maquile en masa sus chips. Recientemente Altera, fabricante “fabless” de FPGAs revocó su contrato con Intel Corporation para que le manufacturara su nueva gama de sistemas de chips programables (SoPC), circuitos con memorias integradas, procesadores embebidos y transceptores de alta velocidad dirigidos a plataformas industriales, sin embargo, por cuestiones de incompatibilidad con la tecnología Tri-Gate de 14 nanómetros propuesta por Intel, Altera decidió optar por TSMC. La decisión de Altera ocurrió solo unas semanas después de que Intel anunciara la alianza comercial entre ambas firmas, divulgada en un reporte de prensa el pasado 26 de abril.

Ranking de principales ‘foundries’.(Fuente: IC Insight).

Posteriormente el pasado 21 de abril Altera publicó en su sitio Web un comunicado en el que revelaba a TSMC como su contratista para la manufactura de su gama de FPGAs “Arria 10” y otros chips SoC. Es decir, en menos de un mes Altera echó para atrás un proyecto que para Intel habría significado una importante línea de ingresos, ya que en el segmento en el que participa, Altera ha demostrado

mantener una diagonal positiva en su diagrama de ventas, tal como lo indica el informe financiero de su primer cuatrimestre de este 2014, liberado en su sitio de Internet. De esta forma, Altera desistió de fabricar sus procesadores FPGAs Tri-Gate de 14 nanómetros de Intel, al proceso FinFET de 16 nanómetros a TSMC.

La manufactura de semiconductores comienza a inclinarse por la tecnología FinFet de TSMC.

La primera diferencia entre ambos procesos de manufactura es la miniaturización más marcada en el caso de la tecnología Tri-Gate de Intel, que maneja su arquitectura a 14 nm, y la cual es considerada como el avance más importante en cuanto a esquemas de producción de dispositivos semiconductores (sensores, procesadores, FPGAs, SoC, MEMS, etc.) a partir de cómo se fabrican los transistores, que son las bases microelectrónicas de todo circuito. Esta tecnología reúne benefactores quienes creen que el Tri-Gate es el siguiente gran paso en la electrónica del mañana, y ahora aparece materializada después de varios años de trabajo de investigación científica.

- PUBLICIDAD -

Object 5

En el caso de la tecnología Fin-FET de TSMC, muchas compañías que trabajan con esta firma taiwanesa, coinciden en que es más estable a nivel microelectrónica para sus productos, principalmente en términos de encapsulado o empaquetado y la fabricación física de su estructura interna, lo cual es importante para todo fabricante que demanda a las fundidoras proteger y respetar sus respectivos diseños.

Tecnología Tri-Gate de Intel.

De acuerdo a los informes, Altera optaría finalmente por FinFET de TSMC por dos razones importantes, en primer lugar, a la demora en la entrega de sus embarques que Intel le ofreció, ya que en estas fechas se manufacturan masivamente sus nuevos procesadores Broadwell, que son prioridad por tratarse de un producto de la casa, a lo que Altera no le combino alegando que cualquier atraso por muy insignificante que fuese, impactaría severamente en la programación de mercadeo. En segundo lugar, durante las casi cuatro semanas que prevaleció el convenio comercial, Altera estuvo muy al pendiente observando los resultados de Intel al manufacturar sus chips con la tecnología Tri-Gate de 14 nm, peor al parecer hubo problemas técnicos en la producción de los Broadwell, que han mantenido ocupados a los ingenieros de soporte e investigación de la compañía, por lo que Altera determinó declinar al convenio y evitar que sus chips sufrieran esas presuntas incidencias registradas. Cabe mencionar que Tri-Gate es una tecnología recientemente lanzada a la industria, y a pesar de que ha sido sometida a diversas pruebas de rendimiento, supuestamente no fue robusta la fase de validación, y como resultado, al momento de implementarla en sus propios productos, Intel destapó involuntariamente la necesidad de afinar o perfeccionar su tecnología. En otro certero golpe a favor suyo, TSMC logró persuadir a Apple para manufacturarle su siguiente gama de chips A8, un procesador ‘quad-core’ de 64 bits con un formato U+GPU, que en un principio la firma de la manzana tenía contemplado producirlo en las fábricas de Samsung. La fuente principal de esta información filtrada a la industria es el diario financiero Comercial Times, de Taiwán, que afirmó haber logrado recolectar datos de una fuente allegada a TSMC que apuntaba a un probable convenio de manufactura industrial con Apple. La decisión de Apple arrastra desde tiempo divergencias con Samsung por presuntos conflictos de propiedad intelectual, situación que ha motivado a la compañía a buscar otros fabricantes para sus circuitos, en este caso TSMC. Estos dos nuevos clientes posicionarían naturalmente a TSMC la capacidad para posicionarse como el principal manufacturero de dispositivos semiconductores de la industria electrónica, y revalidaría

su potencial con los esquemas multimillonarios que ha registrado en los últimos años por concepto de ventas y ganancias. Por ejemplo, en un estudio realizado por la agencia de consultoría IC Insight, TSMC reportó ventas por 19 mil millones de dólares en 2013, lo que superaría sin problema alguno con la adquisición de Altera y Apple a su portafolio de clientes. En la siguiente tabla de IC Insight se enlistan los principales fabricantes fundidores o ‘foundries’, donde se observa a Taiwan Semiconductor Manufacturing Corp., en la posición número uno.

https://www.electronicosonline.com/multi-patrones-secreto-de-la-manufactura-moderna/

Multi-Patrones: secreto de la manufactura moderna abril 2, 2014 Diseño Digital

• • •

Facebook Twitter Google + El fabricante de herramientas EDA, Mentor Graphics reconoce que la fabricación de circuitos electrónicos inferiores a 20 nanómetros, requiere de técnicas sofisticadas como el “Multi-Patterning”. (ElectronicosOnline.com Magazine / Oswaldo Barajas) En la industria electrónica los procesos de manufactura son variables y reacondicionados cada cierto tiempo, a fin de fabricar nuevos circuitos con capacidades suficientes para convertirlos en el corazón de nuevos productos más potentes y eficientes.

Pero una de las técnicas que es utilizada por los manufactureros de estos circuitos modernos con arquitecturas miniaturizadas -por debajo de los 20 nanómetros (nm)- es el “Multi-Patterning”, una técnica que de acuerdo al fabricante de herramientas para el diseño electrónico, Mentor Graphics, es una

de

las

columnas

semiconductores.

primordiales

que

sostienen

la

actual

manufactura

electrónica

de

Para ello, la compañía destinó un artículo técnico para explicar la importancia de Multi-Patrones en el segmento de fabricación de circuitos integrados más vanguardistas. El documento que se titula “Mastering de Magic of Multi-Patterning”, sostiene que esta técnica ha sido introducida para afrontar las limitaciones litográficas de la presente manufactura electrónica. El autor de este material define como “mágico” el resultado que se consigue con la implementación de doble y triple patrón en el diseño de circuitos dimensionalmente más pequeñas, pero también reconoce que es de capital importancia para los ingenieros diseñadores el conocer todos los pros y contras al momento de aplicar esta técnica. Debido a que los fabricantes deben garantizar que cubrirán las demandas de sus clientes, tales como mayor eficiencia energética, reducción de tamaño, mayor funcionalidad y otros aspectos que tienen que ver con el rendimiento de los circuitos electrónicos, los propios manufactureros se han dado a la tarea de encontrar mecanismos que garanticen los nuevos requerimientos de la industria. Cabe mencionar que esta misma situación ha orillado a los fabricantes a desarrollar nuevas herramientas que optimicen sus procesos, siendo algunas de las modas establecidas la integración de litografía convencional sin software, reglas basadas en software OPC, modelos OPC, inserción SRAF, verificación de software OPC, simulación embebida de hardware y software, software SMO (Server Management Objects), software de doble patrón y software de triple patrón o SADP (SelfAligned Double Patterning), por mencionar algunos.

En la anterior gráfica, Mentor representa una de las presuntas tendencias en la manufactura de circuitos

con arquitecturas menores a los 20 nm, siendo la sombreada de color verde y en donde se aprecia también el software relacionado.

Pero estas tendencias que están dirigidas a conjuntar varios recursos en una sola herramienta, ha ido sumándose conforme se reducen las dimensiones nanométricas de los circuitos electrónicos, de esta forma, entre más pequeños sean los dispositivos, más recursos deben de poseer, lo que es significativamente más complejo para quienes diseñan tales componentes. En el mundo de los circuitos electrónicos, el desarrollo de dispositivos utilizando el proceso de doble patrón (DP) tiende a identificarse como el método “Litho-Etch-Litho-Etch” (LELE), con el cual se puede trabajar las capas metálicas del componente, las vías y estructuras activas, en formatos apilados utilizando el esquema LELE DP a 20 nanómetros. Pero en esta fase tan compleja, los fabricantes deben estructurar debidamente todos los elementos para integrarlos en diferentes capas, siendo muy cuidados en su manipulación con las unidades lógicas como los transistores a fin de no estropearlos.

- PUBLICIDAD -

Object 6

El proceso de multi patrones puede otorgar hasta cuatro posibles flujos de diseño.

Por ejemplo, entre los transistores más utilizados para esta clase de manufactura se encuentran los transistores FinFET o de Efecto-Campo. Estas unidades requieren de una capa especial y otras líneas adicionales para que funcionen a cabalidad, y para crear sus líneas complementarias se recurren a técnicas como SADP (Auto-Alineación de Doble Patrón). Pero también existen casos donde el dispositivo que se manufactura es a 10 nanómetros, entonces para estos existen técnicas como SID (Separador Dieléctrico) una variante del esquema DADP donde se utilizan algunas capas metálicas de interconexión para generar las líneas que requiere la estructura conformada por los FinFETs. Como se puede observar en la siguiente imagen, las capas forman una plasta o apilamiento donde se aprecian las interconexiones entre cada una:

Esquema de separación de capas dieléctricas.

De acuerdo al documento de Mentor, la técnica LELE DP provee hasta cuatro posibles flujos de diseño: Descomposición Manual, Descomposición Automática, Descomposición Mixta y Sin-Color. En lo que respecta a las tres primeras opciones, se aprecian flujos de dos colores, donde los diseñadores colocan dos capas de colores por separado para DP o doblemente patroneadas. Pero en la cuarta opción, el flujo de Sin-Color el ingeniero coloca una sola capa y procede con su descomposición. La diferencia entre las tres primeras opciones y la cuarta es el nivel de automatización que utiliza para crear las dos capas (DP). Por ejemplo, en la Descomposición Manual, el diseñador decide cómo implementar el diseño en dos máscaras, estructurar ambas a mano y revisar su viabilidad para el formato de doble capa haciendo uso herramientas tradicionales en reglas de diseño (DRC, por sus siglas en inglés). Pero en el caso de la Descomposición Manual, como su nombre lo dice, requiere de una inversión considerable de tiempo y su nivel es altamente complejo, además de los grandes bloques que involucra el dibujar el flujo, lo que es impráctico, con lo cual no cualquier ingeniero se atreve a inmiscuirse.

En la descomposición sin-color, los ingenieros suelen utilizar herramienta especial para identificar los errores mediante la asignación de colores establecidos.

En la Descomposición Automática, el diseñador dibuja una sola capa y pasa a utilizar herramientas especiales para auto-calibrar la descomposición multi-patrón del diseño y revisar automáticamente su viabilidad en el formato MP. Sin embargo, estas herramientas pueden crear datos de incompatibilidad y errores prematuros de diseño debido a que ejecutan modelos de simulación y validación según sus preferencias automáticas, por lo que suele ser una navaja de doble filo, ya que, o se ahorra tiempo en el diseño o bien se invierte más al identificar los problemas que causó alguna de las herramientas con recursos automáticos. En la Descomposición Mixta, los ingenieros tienden a incorporar células o módulos previamente descompuestos en una nueva capa ya asignada, siendo como una especie de cimiento para que los s eviten la construcción de la base del circuito.

Algunas herramientas más sofisticadas permiten ejecutar en el mismo ciclo de diseño pruebas de validación o simulación que ahorran tiempo y ayudan a descubrir errores en los proyectos de multicapas.

Finalmente en el caso del flujo Sin-Color, el ingeniero dibuja una sola capa y trabaja con formatos especializados de Multi-Patrones para identificar espacios que no pueden ser correctamente descompuestos. De esta manera la capa debe ser modificada hasta que las revisiones salgan limpias de errores, entonces se procede con su descomposición en dos capas después de la implementación Sin-Color. De esta manera existen algunas herramientas que presentan los errores y las incompatibilidades de manera automática asignando colores, donde el puede recurrir rápidamente a la aplicación de soluciones para cada caso. Mentor Graphics reconoce que la técnica de Multi-Patrones es a la fecha uno de los secretos con los que cuenta la industria de semiconductores, y es por tal motivo que expone los beneficios de utilizarla de forma adecuada, incluso conociendo las diferentes herramientas que existen en el mercado, las cuales tienen la capacidad de facilitar las labores de diseño de circuitos integrados a los ingenieros.

https://www.electronicosonline.com/apple-disparara-industria-‘pure-play’-de-semiconductores/

Apple disparará industria ‘pure-play’ de semiconductores septiembre 2, 2013 Industria y Negocios

• • •

Facebook Twitter Google + La firma de la manzana retirará parcialmente la producción de semiconductores que tiene con Samsung y la reasignará a fabricantes “pure-play” como TSMC, lo que elevará hasta 21% en 2013 los buenos pronósticos para el segmento de “solo-fundidoras” electrónicas. (ElectronicosOnline.com Magazine / Oswaldo Barajas) Ante la determinación de Apple para retirar el contrato con Samsung en la fabricación de buena parte de sus chips, la firma de la manzana ha visto en el segmento de compañías ‘pure-play’ o solofundidoras, el apalancamiento pretendido para su estrategia comercial.

En esta acción, el fabricante de los “i-gadgets” inclinará la balanza en un segmento que camina discreto dentro de la esfera de la industria electrónica, compuesto por fabricantes base y fundidores de materias primas para la manufactura de circuitos electrónicos basados en sustratos como Silicio. De

acuerdo

al

portal Apple

Insider,

cuya

principal

fuente

informativa

refiere

al

rotativo

estadounidense The Wall Street Journal, expone que tras una relación de varios años con el fabricante

surcoreano

Samsung,

Apple

decidió

mudar

el

proyecto

de

manufactura

de

semiconductores de esta firma hacia la compañía fundidora Taiwan Semiconductor Manufacturing Co (TSMC). Cabe señalar que la disolución de lo que para muchos fue nombrado un matrimonio corporativo entre Apple y Samsung, dio lugar cuando la empresa surcoreana aprovechó su posición para reproducir supuestamente un módulo digital exclusivo de Apple para favorecer a su gama de teléfonos inteligentes “Galaxy” con tecnología ‘touchscreen’, lo que generó un episodio judicial por violación de propiedad intelectual.

El artículo del WSJ, señala que el contrato laboral de Apple para TSMC determina la concesión de proyectos de manufactura de los chips A-Series SoC de 20 nanómetros para la siguiente generación de iPhone y iPad de Apple.

La decisión de Apple de retirar parcialmente el proyecto a Samsung se debió presuntamente por los conflictos de propiedad intelectual a raíz de que la firma surcoreana aprovechara su posición para integrar un módulo como el de Apple para su gama Galaxy.

La producción de los circuitos por parte de TSMC comenzará a partir del 2014 y en este movimiento se verá reflejado un incremento sustancial en la participación del bloque de compañías ‘pure-play’ o también conocidas como solo-fundidoras.

- PUBLICIDAD -

Object 7

Pero no todo es sombrío para Samsung, ya que Apple, con todo y el conflicto de violación de patente causada supuestamente por la firma surcoreana, mantendrá el proyecto de manufactura de chips ASeries, sin que el periódico haya develado si Apple también planea alguna de derogación de este proyecto a corto o mediano plazo. Los acercamientos de Apple con TSMC comenzaron a principios del 2011, cuando el emporio del acaecido Steve Jobs, ofreció al fabricante taiwanés el proyecto de manufactura de los chips A-Series, el cual fue declinado por directivos de TSMC argumentando que en su momento no contaban con la infraestructura adecuada para manufacturar los semiconductores en los tiempos demandados por Apple, tampoco reunía los estándares requeridos por la firma de la manzana. A este tiempo, el corporativo taiwanés –considerado uno de los principales fabricantes de semiconductores- informó que ya cuenta con capacidad para cubrir los requisitos de Apple y procedió a realizar la logística para comenzar con la producción de los chips de los futuros productos de la compañía estadounidense. Inclina la balanza a favor del ‘pure play’ De acuerdo a la firma de consultoría IHS iSuppli, los pronósticos de crecimiento para el segmento de fabricantes de semiconductores son alentadores. Tan solo para el presente año 2013, se espera que

las ganancias para las empresas que participan en este grupo alcancen los 33 mil millones de dólares (mmdd) y mantenga una constante de crecimiento de aproximadamente 8.6% anual. El sitio de consultoría y análisis industrial adjudicó este comportamiento a la postura de muchas compañías que como TSMC, han flexibilizado su infraestructura y optimizado sus procesos para adaptarse a los nuevos requerimientos de muchas compañías de electrónica como Apple, que buscan empresas manufactureras que ofrezcan la garantía de calidad mediante certificaciones y otros documentos que incrementen la confianza de las compañías de equipo original (OEMs) que entran en el bloque de las ‘fabless’ o sin equipo de manufactura base, como Apple.

Se estima que para el año 2015 la manufactura de chips a través de compañías ‘pure play’ habrá de mantener un buen ritmo de crecimiento.

En los últimos años la industria electrónica ha ido inclinando su producción global hacia las compañías ‘pure-play’ o de solo-fundición, como es el caso de TSMC, y dejando como opción secundaria aquellas que pertenecen al grupo IDM (Fabricantes de Dispositivos Integrados) que ofrecen como su nombre lo indica, un sistema de fabricación integral para las compañías ‘fabless’. No obstante, la opción ‘pure-play’ pretende elevar el nivel de flexibilidad o escalamiento de integración tecnológica para incluir mayores componentes a los productos dentro de su flujo de manufactura, como la adición de memorias NAND flash y otros módulos, lo que les otorga a las compañías OEMs un recurso valioso para configurar a conciencia y de una forma más vigilada sus propios productos.

https://www.electronicafacil.net/tutoriales/Materiales-semiconductores.php

Materiales semiconductores Con la invención de un amplificador de Estado Sólido en 1947, por Shockley, Bardeen, and Brattain, la posibilidad del aumento en la integración en el mismo cristal es una realidad. En las últimas décadas, y hoy en día se aumenta el numero de componentes que se introducen en el mismo cristal. Esta industria es altamente rentable, pero las inversiones en desarrollo son también muy altas, lo que hace que las inversiones sean a la largo plazo. Lo que hace que la industria microelectrónica sea rentable es que su procesos de fabricación (Batch Processing), funcione correctamente. Esto hace que en cada chip sea de 8mm de lado, que hace que en cada oblea tengamos de 120-130 circuitos. Cada oblea es tratada de forma que todos los circuitos se hacen a la vez, pasando por el mismo

proceso en el mismo instante. Aunque hay procesos como el encapsulado y el testéo, que se deben hacer individualmente. -¿Qué semiconductores son aptos para hacer dispositivos electrónicos ? Los elementos del tipo IV (Columna del Silicio), son los más indicados para utilizarlos como semiconductores. Aunque para que funcionen como tal deben de tener un gap comprendido, entre 0.5 y 1 eV aproximadamente. Aunque como bien se sabe ya el Gap de un semiconductor se puede variar añadiendo impurezas a este. Pero no solo los elementos de la columna IV, son candidatos a buenos semiconductores, sino la combinación de los elementos de las columnas de al lado la III y la V, también lo son. P.e. GaAs Ga| Ge | As También otros dos elementos que se combinan como buenos semiconductores, es el GaP. Los elementos del grupo IV-VI, también se combinan formando semiconductores de Gap muy pequeños, pero de enorme importancia en el ámbito militar, y en la detección de infrarrojos. P.e. PbSe (Galena) De todas maneras, son pocos los elementos, los cuales los podemos hacer crecer como cristales. Ahora vamos a hacer una breve historia de los dispositivos electrónicos : 1904- Primer detector de Ondas de Radio (Unión metal-PbSe) 1940-1945 Se desarrollan en Alemania. Detectores de radiación (Térmica) Aplicación en la detección de aviones. 1547 Transistor Bipolar (Germanio) 1959 Circuitos Integrados 1961 Tecnología planar desarrollada por Fairchild Semiconductor 1963 MOSFET- Aunque la idea era anterior, por problemas tecnológicos no se pudo desarrollar ( Creación de el óxido semiconductor) -Conceptos Industriales de Producción de CI Custom : El fabricante lo hace todo hasta la última máscara, y los transistores con su colocación y conexión. ASIC : Circuitos muy específicos que el fabricante no hace, por no tener asegurado un mercado (Es una relación entre cliente y fabricante, mucho más directa y las inversiones empresariales son mucho menores). Tamaño mínimo 0.4 m, esto viene dado porque la longitud de onda de la luz utilizada para las máscaras oscila entre 0.3 y 0.7 m m. y se producen fenómenos de difracción óptica, proceso que impide la buena realización fotolitográfica. -Los procesos de introducción de dopantes ha pasado por 4 tipos de fabricación básicamente:

Aleación: El dopante que queremos introducir se pone en o con el semiconductor, a los cuales se le pone a una temperatura alta para poderse producir la aleación. El dispositivo ocupa un 1% del espesor total de la oblea, por tanto hay un 99% que no se aprovecha, esta zona "muerta" además da problemas de funcionamiento del dispositivo. .-Problemas: *No se controla la introducción de dopantes *Se tiene que reducir la zona muerta. Difusión: La física del proceso es la misma, que en el caso anterior, pero tenemos un control mucho mayor sobre él. En este caso el dopante está en forma gaseosa, para introducirlo en las zonas que queremos dopar. .-Problemas: *Interconexiones entre los dispositivos. *Sigue existiendo zonas muertas. *El control debería ser mayor sobre las zonas a dopar. Difusión Planar-Epitaxial: Partimos de un cristal fuertemente dopado, al cual se le hace crecer una capa epitaxial, de semiconductor con un dopado menor. Posteriormente se oxida el Si, de forma que obtenemos SiO2. Se abren huecos en el óxido para que las impurezas entren donde nosotros queremos: El dopante se introduce en todas las direcciones de forma que no es igual el área de la superficie a la proyectada. Con este proceso hemos resuelto el problema de la zona muerta. .-Problemas: *Difusión lateral *Si las dimensiones se reducen la difusión lateral puede hacer que tengamos una unión en los dispositivos. Implantación Iónica: El proceso es totalmente análogo al anterior pero cambiamos la tecnología utilizada en la introducción de los dopantes. Las impurezas se aceleran utilizando potenciales de 100000 V. Pudiendo controlar perfectamente variando la energía de los iones los lugares donde queremos introducirlos. Crecimiento de Cristales El primer problema que tenemos es conseguir Si con un alto grado de pureza, para poder fabricar Si cristalino. La densidad efectiva de átomos debe ser 10 23, para el purificado se hace reaccionar con

clorhídrico en fase vapor, y después de varias reacciones (Destilación fraccionaria), obtenemos lo que se llama Si electrónico. Una vez conseguido esto ya podemos darle una estructura cristalina. Método Czochralski : En una atmósfera controlada e inerte, tenemos una cubeta de grafito o cuarzo (que funden a temperaturas 3000 ºC En la cubeta se introduce Si electrónico . El cilindro está rodeado de una bobina de alta frecuencia y alta corriente, con esto se funde el Si (1240 ºC). Se introduce en el Si fundido una pértiga con una semilla de Si cristalino, el cual por capilaridad se une a la semilla, formándose Si cristalino alrededor de la semilla, de forma que tirando y girando la pértiga hacemos crecer el cristal. (5 a 6 pulgadas de diámetro). Este método así realizado tiene un problema y es que las paredes de cuarzo o de grafito, introducen impurezas en el Si cristalino que se forma, porque al estar toda la cubeta a una temperatura alta se producen deterioros en esta. Para evitar esto se va utilizar el método de la zona flotante, en el cual la bobina no está en todo el cristal sino únicamente en una zona muy concreta alrededor de la semilla, esta bobina es móvil y según movemos la semilla la bobina la acompaña. El problema que tenemos ahora es que hay un alto número de dislocaciones debido al gradiente térmico. El lingote de Si cristalino se corta en obleas, perdiéndose en el proceso la mitad del Si. Luego viene un proceso de redondeado y de pulido. Procesos de Dopado Difusión : La introducción de dopantes en Si como se produce a partir de una fase gaseosa, lo cual hace que la ley que rige el proceso sea la siguiente :

Donde C es la concentración de impurezas, y D el coeficiente de Difusión, que depende del material del dopante. Las temperaturas a las cuales nos movemos para estos procesos rondan los 1000ºC. Hay un problema en los procesos de difusión y es que la temperatura hay que controlarla muy bien, dado que sino la concentración de impurezas puede variar bastante en tan solo 50 ºC. Tenemos un límite de solubilidad que es la máxima concentración del dopante que ite el Si. -Etapas del proceso de dopado por difusión : 1ª. Etapa : Predepósito Se genera una presión de vapor de la impureza que queremos introducir. Condiciones de contorno de la ec. de difusión.

C(0,t)=C s ; Ct)=0 ; C(x,0)=0 Donde la solución para la ecuación de difusión es :

donde la función erf c (x) cumple las siguientes propiedades : erf c(x)=1-erf(x)

donde erf(0)=0 y erf ( ¥ ) Por tanto el número de impurezas introducidas, por cm 2 en tiempo son :

2ª Etapa : Redistribución Una vez situadas las impurezas en el proceso de predepósito, retiramos la fuente gaseosa que contiene el dopante. Posteriormente estas impurezas se redistribuyen durante un tiempo y a una temperatura determinada. Por tanto las condiciones de contorno para nuestra ecuación de difusión son las siguientes :

Donde D 2=Coef. de difusión a la temperatura de redistribución, y t 2 el tiempo de redistribución. Se puede determinar la posición de una unión cuyo dopado ha sido realizado por difusión.

Fig: La posición nos la da la siguiente ecuación : N A(x j,t)=N D donde N A(x j,t) es : N A(x j,t)=

si ha habido predepósito

N A(x j,t)=

si ha habido redistribución.

Ej . : Sobre una oblea de n-Si (N D=10 15 cm -3) se predeposita Boro con los siguientes datos : C s=10 18 cm -3 ; T 1=1000 ºC, t 1= 5 min. Después de este proceso se redistribuyen a T 2=1200 ºC durante t 2=2 horas. Encontrar : •El perfil de Impurezas •Posición de la unión. Implantación Iónica : Es un proceso de alto vacío en el cual introducimos dopantes en un sólido a partir de haces de iones, fuertemente acelerado, de la impurezas que queramos usar. -Hay procesos de colisión , con lo cual hay desviaciones en los iones. También se produce el efecto contrario que es la rotura de los átomos de la red en la zona de impacto, generando vacantes en la estructura cristalina. -El perfil de dopado de las impurezas dentro del cristal cumple una ley gaussiana de probabilidad, de tener una concentración en un lugar geométrico x,y,z. -Una vez obtenido el perfil hay que reordenar la red mediante un recocido para que los iones de la red se coloquen en sus posiciones originales, y de vez en cuando un ion implantado se coloque en la posición de un ion de la red. (Si la concentración de dopantes fuera análoga a la del semiconductor tendríamos una aleación. -Ventajas de la Implantación Iónica : Separación de masas : No tenemos dopantes que no deseamos, dado que separamos muy bien los iones, como luego se verá en el montaje del sistema. Como tenemos un entorno de vacío, tenemos ausencia de contaminantes. Como el proceso lo realizamos a baja temperatura evitamos la redistribución de las impurezas, cosa que nos haría perder nuestros perfiles de dopado, y mantenerlos todo lo abruptos que queramos. -Inconvenientes de la Implantación Iónica : Dañado : El ion implantado destruye la red cristalina, y por tanto necesitamos recocidos de recristalización (RTA). Esto tiene un problema y es que pueden producir redistribuciones en las impurezas, esto no ocurre si el tiempo del recocido y el coeficiente de Difusión de las impurezas

dentro del semiconductor no es demasiado alto. Por eso se utilizan hornos que alcanzan alta temperatura en un intervalo de tiempo muy corto. Costo del equipamiento. Oxidación Térmica, Litografía y Grabado Oxidación Térmica: Consiste en el crecimiento de una capa de SiO 2 sobre una superficie de Si a expensas de este. Hay dos tipos de hacer este óxido, en atmósfera seca O 2 o húmeda (H 20) a una temperatura elevada ( ~1000 ºC) La oxidación seca es bastante lenta pero produce un óxido de excelente calidad, que es muy usado en las tecnologías MOS para el óxido de puerta. La oxidación húmeda es bastante más rápida pero produce un óxido de mucha peor calidad, con porosidades, el cual solo sirve para procesos de enmascaramiento. Aplicaciones del SiO 2 : Máscara de protección para procesos de dopado=>Dopados Selectivos.(0.3 m m de espesor aproximado) Óxido de puerta en estructuras MOS Óxido de Aislamiento en tecnologías LOCOS (Local Oxidation Silicon ) Pasivación eléctrica de superficies Modelo Elemental del Proceso de Oxidación : La atmósfera oxidante se satura de manera que la concentración de oxidante en la superficie de SiO 2 es la de máxima solubilidad N 0. El oxidante se difunde a través del SiO 2 formado y llega a la interfase SiO 2 -Si en concentración N 1< N 0 donde reacciona con el Si y se forma SiO 2. Flujo de oxidante a través del óxido :

donde D es el coeficiente de Difusión en SiO 2 del O 2 y del H 2O. El flujo de oxidante que llega a la interfase SiO 2-Si es el siguiente : F 2=kN 1, donde k es la velocidad de reacción superficial. La situación estacionaria la tenemos cuando el SiO 2 no es fuente ni sumidero de oxidante por tanto estamos en un proceso de equilibrio : F 1=F 2=F

En esta situación tenemos que el flujo nos queda lo siguiente :

Tenemos por tanto que la velocidad de crecimiento del óxido con la condición inicial x 0(t=0)=x i (~40 Å)

Tenemos que la solución es :

donde : A=2D/k B=2DN 0/N 1 t =(x i 2+Ax i)/B Podemos observar dos resultados principales de la expresión obtenida que son : -A tiempos cortos de oxidación, el proceso viene limitado por la velocidad de oxidación superficial del Si. -A tiempos largos de Oxidación, el proceso viene limitado por la difusión de oxidante a través del SiO 2 . Ej. : Demostrar utilizando la expresión obtenida las dos afirmaciones anteriores. Litografía y Grabado Se refieren a los procesos de transferencia de los motivos, que dan lugar al circuito integrado, sobre la oblea del semiconductor. La litografía es la exposición de motivos a través de máscaras convenientemente diseñadas y el Grabado es la eliminación selectiva de óxidos, metales, etc Estos procesos son los que nos marcan la tecnología en la construcción de C.I., y por tanto una avance en estos procesos permite una evolución en la tecnología de integración. El proceso litográfico consta de los siguientes pasos : -Una vez generado el óxido del Si, sobre el semiconductor, colocamos una capa de Fotorresina sobre el óxido. -Una vez hecho, hacemos pasar luz (UVA), a través de una Máscara, el cual se proyecta sobre la fotorresina.

- La fotorresina ha quedado impresionada por la proyección hecha en el proceso anterior. Y la introducimos en un compuesto el cual elimina la zona impresionada (Positivo), o la que no lo está (Negativo). El Inversor CMOS Hoy en día la gran mayoría de los circuitos integrados de Aplicación específica, utilizan tecnología CMOS. La cual se nutre a su vez de los transistores MOS (Metal Óxido Semiconductor), los cuales vamos a empezar estudiando para entender las bases de funcionamiento tanto en el aspecto estático como en el dinámico. 2.1. El transistor MOS Representamos a continuación circuitalmente un transistor MOS de canal n, cuyas conexiones son: -Puerta G -Fuente S -Drenador D Y sean VG, VS y VD, las diferencias de potencial entre dichas conexiones y el substrato de Si, tipo p sobre cuya superficie se ha integrado el transistor. El funcionamiento del dispositivo es sencillo: -Mientras la tensión VG es menor que un valor mínimo, corriente que circula entre el drenador y la fuente es despreciable. -En cambio si sobrepasamos el valor mínimo de VG, se crea un canal de inversión tipo n, entre la fuente y el drenador. Si la tensión VD es mayor que VS, circulará una corriente entre ambos que llamamos IDS. Tenemos que hacer un estudio detallado de la tensión umbral en un punto del canal, que es el valor mínimo de la tensión VG para que la zona de inversión se mantenga dicho punto del canal. Este valor depende de la diferencia de potencial V, entre el punto del canal considerado y el substrato. (Ver figura de la variación de la tensión umbral con (VT, V). Un resultado importante que podemos obtener es el de la densidad de cargas libres en un punto del canal del MOS. Como ya sabemos la Capacidad de un condensador viene dada por la expresión C=Q/V, viendo que en el transistor MOS entre el o metálico y el semiconductor tenemos un condensador, con lo cual aplicando lo antes dicho, podemos deducir que: s =C ox[VG-VT(V)] (1) donde C ox es la capacidad por unidad de superficie del condensador formado por la puerta, el óxido y el canal [Faradios/m 2]. Y V es como antes dijimos la diferencia de potencial entre el punto considerado y el substrato. Vamos a entrar ahora en el Cálculo de la Corriente que pasa por el canal del transistor. Si tomamos como la superficie en la cual vamos a hacer nuestro estudio, como una zona del canal de longitud

infinitesimal dx y de anchura W . Aplicando estos datos en la ecuación anterior (1), obtenemos que el valor dQ de cargas libres en el canal son las siguientes: dQ=dxWC ox[VG-VT(V)] Sabiendo que el campo Eléctrico en esta zona es igual a : E=dV/dx y que la velocidad de desplazamiento de los electrones viene dada por el producto de la movilidad de estos, por el campo Eléctrico aplicado. v= m n dV/dx Por tanto como conocemos la velocidad y la distancia que tienen que recorrer podemos calcular el tiempo de tránsito de los electrones. t=dx/v=(dx) 2/ m n dV (2) Y por tanto la corriente que atraviesa el canal es la siguiente, y utilizando las ecuaciones 1 y 2 I= dQ/t I dx = m n W C ox[VG-VT(V)] dV Si despreciamos las corrientes de fuga, lo cual nos hace considerar que la corriente a lo largo del canal es la misma. Integramos la anterior relación, obteniendo la siguiente expresión:

donde a la parte de la integral la llamamos S, y en la siguiente figura podemos ver el significado físico de la expresión. -C ox depende del proceso de fabricación ( e /z), S también y del valor de las tensiones empleadas. Corriente de Saturación Todo este proceso es válido siempre que no supere VD el valor VDP. Si tenemos el caso en el cual coinciden estos dos valores, tenemos que la tensión de puerta es igual a la tensión umbral, con lo cual, dicha tensión de puerta no puede mantener los portadores libres en el canal cerca del drenador. Este fenómeno se le conoce con el nombre de Pinch-Off o estrangulamiento del canal. Se produce por tanto una zona de empobrecimiento en la cual no existen portadores libres, y todo aumento en la tensión del drenador cae en esta zona. El potencial en la zona de canal que aun tiene portadores sigue siendo VDP. Por tanto el potencial en el canal viene dado por la diferencia de potencial entre la fuente y la zona de estrangulamiento (VDP). Si suponemos que la longitud del canal entre la fuente y la zona de estrangulamiento prácticamente no se modifica, podemos considerar que la corriente entre el drenador y la fuente IDS, permanece invariable. Por lo tanto como hay una diferencia de potencial existe un campo eléctrico, de valor : (VD-VDP)/l

que nos hace conducir los electrones al drenador. Por lo tanto cuando VD>VDP la corriente IDS toma un valor constante : IDSsat= m n . C ox (W/L) Ssat Donde Ssat es la superficie representada en la siguiente figura : Podemos obtener la curva IDS en función de VDS, y ver que se comporta como una resistencia, función de la tensión VD. 1/R=dIDS/dVD= m n . C ox (W/L) dS/dVD El valor de dS/dVD se deduce directamente en la siguiente figura : dS=hdVD Con lo cual dS/dVD=h, con lo cual la resistencia es proporcional a 1/h, según aumenta VD disminuye h, y por tanto aumenta la resistencia, hasta que alcanza un valor infinito cuando el transistor esta saturado. Con lo cual la curva IDS, VDS (VD-VS), para un valor fijo de las tensiones VG y VS. El Transistor MOS de Canal P El estudio del transistor MOS tipo P es análogo al hecho en el caso de los tipo N. Al igual que antes los potenciales se definen en función del substrato que utilizamos en este caso tipo N. En este caso como ya se podía esperar las tensiones VG, VS y VD son negativas. Por tanto el proceso de funcionamiento es el siguiente cuando tenemos una tensión VG menor que la tensión VT (Que también es negativa), un canal tipo P aparece entre el drenador y la fuente, si además hay una diferencia de potencial entre el drenador y la fuente, aparece una corriente ISD entre estos dos puntos. Tanto en el transistor de canal N como en el de canal P, los portadores van siempre del drenador a la fuente, aunque en el caso de las corriente van en sentidos contrarios. (n=IDS y p=ISD). El símbolo del transistor p lo tenemos a continuación, junto con su estructura física : Las expresiones son análogas que en el caso anterior, pero donde antes teníamos la movilidad m n ahora tenemos la de los huecos m p . Por tanto la corriente ISD es la siguiente : ISD= m p . C ox (W/L) S Siendo S la superficie representada en la siguiente figura : Si VD(< ó =)VDP, entonces el transistor está saturado, con lo cual la corriente es : ISD sat= m p . C ox (W/L) S sat Donde la superficie S sat viene dada en la siguiente figura :

El Inversor : Vamos a estudiar ahora el elemento más importante dentro de la microelectrónica actual como es el inversor CMOS, cuyo esquema se representa en la siguiente figura. Como se ve se tiene que contar con dos substratos : •Uno tipo p, conectado a VSS voltios, cobre la cual se pone el transistor de canal n •Otro tipo n, conectado a VSS+VDD, sobre cuya superficie se integra el transistor de canal p. Funcionamiento Estático : Ahora vamos a suponer que todas las tensiones se miden con respecto a la tensión VSS, que la hacemos 0 voltios. Dentro de las tensiones umbrales de los dos transistores , supondremos a su vez que: VT0n< VDD+VT0p Supondremos también que en el funcionamiento estático la corriente de salida será nula: IOUT=0 A Que corresponde al caso en que a la salida tengamos un condensador, y que esté en estado estable. (Ver siguiente figura) Vamos a ver los posibles casos que se pueden dar en esta configuración: •VIN< VT0n se puede ver en la siguiente figura, el transistor de canal n esta en corte porque no ha sobrepasado la tensión umbral. Como la corriente de salida debe ser cero, tenemos que tener que la tensión de salida debe ser VDD, para que la corriente en el transistor de canal p sea igual a 0 (IOUT=0). •Si VIN>VDD+VT0p, entonces podemos ver ahora el canal p, es el que está en corte. Por tanto ahora la tensión de salida debe ser 0 para que no pase corriente por el transistor de canal n, y por tanto IOUT=0. •Tenemos otro caso en el cual, se pude demostrar que hay un valor de Vinv ,tal que la salida pueda ser cualquiera comprendida entre VDPn, y VDPp, este valor es el que define dos superficies de integración Sp y Sn, tales que: m n . C ox (W n/L n) Sn= m p . C ox (W p/L p) Sp Con lo cual los dos transistores dan la misma corriente, y por tanto a la salida tenemos que de nuevo IOUT=0 •Si VT0n< V inv entonces como podemos ver en la siguiente figura el transistor de canal n está en saturación, y el de canal p se encuentra en conducción. El valor de VOUT lo podemos deducir de las expresiones estudiadas en los puntos anteriores. •Si V inv<<

-Como se puede ver en las expresiones anteriores la tensión V inv depende del valor relativo de las dimensiones de los dos transistores: (W n/L n)/ (W p/L p) También, podemos ver la corriente Interna en función de la tensión de entrada Vin. Como podemos ver solo hay paso de corriente en el intervalo del cambio de on-off, que es cuando tenemos una IDS. El valor máximo viene dado por los valores de las corrientes IDSn e IDSp, calculadas con anterioridad. Funcionamiento Dinámico Normalmente en un circuito integrado las salidas y las entradas de los inversores se conectan a otros inversores, o a otras puertas lógicas. Entonces para hacer el estudio dinámico, debemos hacer algunas modelizaciones. La itancia de entrada se aproxima con un condensador de valor constante. Por tanto despreciamos: La corriente de entrada continua de los transistores. La variación de la capacidad de entrada con la tensión de entrada. Por tanto el cálculo de los tiempos de salida lo hacemos a partir del siguiente esquema: a)Tiempo de Subida: Suponemos que VIN=VSS y que la tensión de salida es V voltios. En las siguientes figuras vemos el significado de los valores Sp(V) y Sn(V). En este estado, sabemos que el transistor de canal n está en corte, y por tanto el único que conduce es el p. Con lo cual la corriente que pasa por el CMOS, es la siguiente : I= m p . C ox (W p/L p) Sp(V) Y recordando la relación vista : dt=dQ/I=CLdV/[ m p . C ox (W p/L p) Sp] Por tanto el tiempo necesario para pasar de una tensión V L a una V H es el siguiente :

t=[ CL/[ m p . C ox (W p/L p)] Análogamente podemos calcular el tiempo de bajada del CMOS, en este caso es el transistor de canal p el que está en corte, y el n conduce, con lo cual el tiempo que nos sale es :

t= CL/[ m n . C ox (W n/L n)]

Consumo : Como pudimos observar cuando vimos la corriente interna que pasaba por el CMOS, era en el momento de la conmutación, cuando el paso de corriente era mayor. Por tanto como sabemos la potencia consumida es función de la intensidad, con lo cual tendremos un mayor gasto de potencia, cuando tenemos conmutaciones (Pasos de altas a bajas, y viceversa)

http://www.tecnicaindustrial.es/TIFrontal/a-4198-nuevos-materiales-fabricacion-dispositivoselectronicos.aspx

Nuevos materiales para la fabricación de dispositivos electrónicos Francisco Javier Balbás García

Vota Resultado 114 votos

Comentarios - 4 New materials for the manufacture of electronic devices RESUMEN En este artículo se presentan las características, prestaciones y posibles aplicaciones de algunos materiales, bien de última generación (caso del carburo de silicio) o bien en vías de investigación (caso del grafeno) para la fabricación de dispositivos electrónicos. Se trata de unos materiales que abren nuevas posibilidades y vías de desarrollo a los diseñadores industriales. Recibido: 23 de abril de 2011 Aceptado: 30 de junio de 2012 Palabras clave Electrónica, materiales, silicio, grafeno, semiconductores,

transistores, telecomunicaciones, dispositivos electrónicos ABSTRACT This paper presents the characteristics, benefits and possible applications of some materials, good art (the case of silicon carbide) or in the process of investigation (the case of graphene) for the manufacture of electronic devices. Materials open up new possibilities and developing ways for industrial designers. Received: April 23, 2011 Accepted: June 30, 2012 Keywords Electronics, materials, silicon, graphene, semiconductor, transistors, telecommunications, electronic devices La mayoría de los progresos tecnológicos coinciden en el tiempo con el descubrimiento o desarrollo de un nuevo material o dispositivo que aporta nuevas posibilidades implanteables hasta ese momento, facilitando el alcance de nuevas metas y funcionalidades. En la actualidad, el material empleado en la mayor parte de los dispositivos electrónicos es el silicio. El silicio es el componente principal de la mayoría de los dispositivos semiconductores, dado que presenta unas características muy apropiadas, entre las cuales se encuentran: – La abundancia significativa del material. – ite un rango de temperaturas muy aceptable respecto la temperatura ambiente, particularidad determinante frente a la máxima temperatura que ite el germanio. – Tiene una tecnología de fabricación muy desarrollada que consigue rendimientos superiores al 95% para obleas de hasta 12 pulgadas de diámetro (Semiconductor Solutions, n.d.). Es un factor muy importante en la actualidad, dado que algunos fabricantes de dispositivos semiconductores fabrican simultáneamente varios tipos de dispositivos en cada proceso de fabricación. Además, se produce una mayor cantidad de dispositivos. Debido a esto, las obleas de mayor tamaño ofrecen, mayor versatilidad, un mayor rendimiento del proceso de fabricación y permiten a los fabricantes de semiconductores reducir los costes de producción en un volumen mayor de productos terminados. Con estas características, el silicio ocupa casi toda la totalidad del mercado. Aun así, esto no quiere decir que con el silicio se consigan unas prestaciones óptimas, pues

una vez descritos los beneficios aportados, también aparecen las limitaciones. Este estudio plantea, con algunos ejemplos, la posibilidad de otros materiales que existen en el mercado (es el caso del carburo de silicio) o que están en investigación (como el grafeno) y que amplían enormemente las posibilidades de aplicación y desarrollo de los sistemas eléctricos y electrónicos de potencia. La mayor problemática de estos materiales reside en su proceso de fabricación. En el caso del carburo de silicio, se ha desarrollado una breve exposición de algunos de los dispositivos existentes en el mercado y sus aportaciones a los circuitos electrónicos. Así mismo, se ha llevado a cabo un estudio práctico para el caso del convertidor Buck-Boost. Por último y englobando todo lo expuesto anteriormente, en el apartado de conclusiones, se presentan varias premisas y posibilidades para futuros diseños de sistemas y nuevas aplicaciones que pudieran aparecer, utilizando los materiales a los que se ha hecho referencia. Materiales Carburo de silicio El carburo de silicio (SiC) es un material complicado de encontrar en el entorno de forma natural. Los primeros antecedentes de su existencia datan de finales del siglo XIX, cuando el investigador Henri Moissan se encontraba examinando rocas de un meteorito. Casi al mismo tiempo, en 1893, Edward Goodrich Achenson, mientras trataba carbono con corindón, descubrió la presencia de un material cristalino muy duro de color negro azulado. Se pensó que este material obtenido fuera un compuesto de carbono y corindón, por lo que se denominó carborundum’. Actualmente, todo el carburo de silicio utilizado es obtenido mediante síntesis. Y uno de los métodos más simples para su obtención es con una combinación de arena de sílice y carbono en un horno de grafito, denominado de Achenson, a temperaturas entre el intervalo de 1.600-2.500 ºC. En la actualidad y debido, entre otras muchas razones, a la gran dureza que le caracteriza, la principal utilización del carburo de silicio es como material abrasivo, pero su aplicación en dispositivos electrónicos se encuentra en avanzado estudio y desarrollo. Existen alrededor de 250 presentaciones cristalinas

similares de carburo de silicio denominadas polytypes. Los principales polytypes de SiC para su utilización como semiconductor son las estructuras 4H y 6H. Estos semiconductores están caracterizados por unas propiedades que los hacen muy atractivos para su aplicación en electrónica de potencia. Entre estas propiedades (SiC Power Transistors, n.d.) se encuentran: – Una elevada conductividad térmica 3,3 (W/cmK) para el SiC-4H y 4,9 (W/cmK) para el SiC-6H. – Alta densidad de intensidad máxima. – Significativa resistencia de ruptura ante elevados campos eléctricos. Propiedades que hacen obvias las ventajas que presenta el carburo de silicio frente al silicio. Con todo, la inmadura y complicada tecnología de fabricación de dispositivos electrónicos en SiC implican que su utilización repercuta en un coste excesivo. Algunos problemas de los procesos de fabricación del carburo de silicio se encuentran en: – Los significativos problemas que conlleva la aparición de dislocaciones y micropipes que afectarán indeseablemente a la fabricación y que serán tanto más abundantes cuanto mayor sea el tamaño de la oblea (Performance-Limiting Micro-pipe, 1994). El cristal sufre tensiones internas y externas que causan el crecimiento de los defectos o dislocaciones. Micropipes se denominan las dislocaciones lineales extendidas en forma de tornillo, transversalmente a lo largo del cristal. – Dificultades con la interfaz entre SiC y SiO2, las cuales han complicado el desarrollo del MOSFET y el aislamiento de la puerta en los transistores bipolares. – Problemas en los os óxidometal a altas temperaturas. – Por otro lado, al ser el tamaño de las obleas menor que las utilizadas con el silicio, no se pueden aprovechar totalmente los equipos de fabricación ya existentes. Además, por lo comentado anteriormente, el rendimiento o aprovechamiento de la oblea en su fabricación es muy reducido, del orden del 15% frente al más del 90% obtenido mediante el silicio. En los últimos años se desarrollan múltiples estudios de investigación y se tiene gran interés sobre la tecnología del SiC. Se han generado múltiples patentes sobre su tecnología de fabricación y se han celebrado congresos y conferencias internacionales.

Aplicaciones del carburo de silicio En la actualidad, en el mercado se encuentran dispositivos de SiC mediante los cuales se pueden optimizar determinados circuitos o funciones. A continuación, se van a comentar algunos de ellos y sus prestaciones. Posteriormente, se presentará un estudio práctico de aplicación para el convertidor Buck-Boost. Para la presentación de dispositivos de carburo de silicio se han tomado como referencia las siguientes empresas; en primer lugar, SiCed a Siemens (SiC Power Transistors, n.d.), la cual presenta diodos de barrera Schottky y el dispositivo de conmutación VJFET, y en segundo lugar, la empresa TranSiC (Power Transistors, n.d.), con el transistor BicSiC. Dichos dispositivos se detallan a continuación: – Diodos Schottky de SiC. Dispositivos que tienen excelentes características de conmutación. Con los diodos de SiC se han obtenido tensiones de bloqueo de hasta 3.300 voltios. Además, se puede trabajar a frecuencias altas, dadas sus particulares características de recuperación. Y, por otro lado, se reducen tanto las pérdidas en el diodo como en la conmutación. – Una combinación en cascada de un MOSFET de silicio y un VJFET de carburo de silicio proporciona un dispositivo con buenas cualidades de conmutación. Posee las características de entrada del MOSFET de baja tensión y la capacidad de bloqueo la aporta el VJFET utilizado. – Transistores de carburo de silicio. Según la empresa TranSiC (Power Transistors, n.d.), utilizando transistores de carburo de silicio BitSiC se obtienen las siguientes cualidades: • Altas temperaturas de trabajo. • Obtención de alta eficiencia con un tamaño reducido y a alta temperatura. • Diseño compacto. • Tolerancia ante la exposición a radiaciones. Aplicaciones directas de los dispositivos comentados se obtienen con la simple sustitución de los componentes críticos de un circuito determinado por unos dispositivos adecuados de carburo de silicio con las características apropiadas para la función a desempeñar por el circuito. Como ejemplo, se tiene, el convertidor Buck-Boost, reductor-elevador (sin transformador de acoplamiento, aislamiento). Si se desarrollan los valores de las tensiones