Flip-flop Sr E Jk 133y4e

This document was ed by and they confirmed that they have the permission to share it. If you are author or own the copyright of this book, please report to us by using this report form. Report 2z6p3t

Overview 5o1f4z

& View Flip-flop Sr E Jk as PDF for free.

More details 6z3438

- Words: 722

- Pages: 6

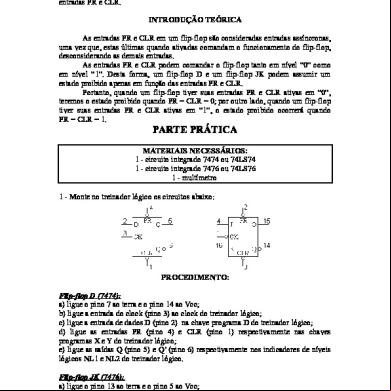

Introdução teórica:

Flip-Flops tem em seu circuito suas variáveis de entrada, uma entrada para o clock e duas saídas, normalmente denominadas com Q e Q’. Quando falamos de clocks e circuitos seqüências, temos que entender apenas um conceito muito simples, que as saídas se alteram de acordo com a entrada apenas quando damos um pulso no clock. Como você já pode notar os Flip-Flops são circuitos seqüências lógicos desenvolvidos para inúmeras aplicações, como por exemplo o controle de alguma produção industrial, onde temos varias entradas que devem funcionar de acordo com um determinada lógica para que a produção possa ser otimizada e nunca parar. Com isso em mente, podemos ver os tipos de Flip-Flops Flip-flop S-R Sincrono

Consiste no tipo mais básico de Flip-Flop, onde temos as duas saídas Q e Q’ e suas variáveis de entrada são um Set e um Reset, onde o Set seleciona o nível lógico 1 na saída do circuito (Q) e o Reset que seleciona o nível lógico 0 na saída (Q’). Abaixo temos seu circuito equivalente. Adote Q como a entrada atual do circuito RS Básico.

Tipo RS com Entrada Clock

Partindo da mesma lógica do tipo de Flip-Flop RS Básico, a única alteração em sua composição é a entrada de um clock, que é a peça fundamental para o circuito, pois quando ativo ele altera a saída de acordo com as variáveis de entrada. Abaixo segue o circuito equivalente.

Flip-flop J-K

O flip-flop J-K aprimora o funcionamento do flip-flop R-S interpretando a condição S = R = 1 como um comando de inversão. Especificamente, a combinação J = 1, K = 0 é um comando para ativar (set) a saída do flip-flop; a combinação J = 0, K = 1 é um comando para desativar (reset) a saída do flipflop; e a combinação J = K = 1 é um comando para inverter o flip-flop, trocando o sinal de saída pelo seu complemento. Fazendo J = K o flip-flop J-K se torna um flip-flop T.

Operação do Flip Flop JK

Tabela Verdade

J

K

Qpróx

Comentário

0

0

Qanterior

mantém

0

1

0

reset

1

0

1

set

1

1

Qanterior

alterna

1º Experiência: Objetivo: Entender o funcionamento do Flip-flop R-S.

Materiais:

Protoboard; Jogo de chaves; Multímetro; CI 7400; 2 leds vermelhos; Fios; Cabos banana; Ponta de prova; Fonte MPL-3303M

Procedimento: Montamos o circuito de acordo com a apostila do laboratório de eletrônica. Após o circuito montado realizamos os testes propostos na mesma apostila, e obtivemos os seguintes resultados .

Resultados: CLK

S

R

Qn+1

Qn+1’

0

X

X

Qn

Qnbarrado

Memória

1

0

0

Qn

Qnbarrado

Memória

1

0

1

0

1

Reset

1

1

0

1

0

Set

1

1

1

1

1

Indeterminado

Tabela1: Resultado do funcionamento do do circuito Flip-flop R-S

Figura 1: Montagem do circuito

Conclusão: Concluímos através deste experimento que os estados do flip flop( set, reset, memória e indeterminado), apresentado pelo professor em sala de aula, foram comprovados a partir do circuito montado em laboratório, onde, por exemplo, todos os estados SET e RESET estiverem em zero e o clock desabilitado o estado Qn+1 permanecera igual a Qn, isto foi observado através dos led´s do circuito.

2º Experiência: Objetivo: Entender o funcionamento do Flip-Flop JK.

Materiais:

Jogo de chaves; Jogo de botões; Multímetro;

Pontas de prova; 2 leds; Cabos banana; CI 7473; Protoboard; Fios; Fonte MPL- 3303M.

Procedimento: Montamos o circuito JK de acordo com a apostila fornecida em laboratório, verificando a pinagem do CI para efetuar as ligações, após a montagem obtivemos os resultados demonstrados abaixo.

Resultados: CL K 0

J

K

Q

Qbarrado

Estado

-----

------

Q0

Memória

1

0

0

Q0

1 1 1

0 1 1

1 0 1

0 1 Q0barrad o

Q0barrad o Q0barrad o 1 0 Q

Tabela 2: Resultado do funcionamento do Flip-flop JK

Figura 3: Circuito montado do flip-flop JK com o CLK em 1.

Memória Reset Set Mem. Invertida

Diagrama de tempos do flip-flop J-K

Conclusão: Concluímos através deste experimento que os estados do flip flop( set, reset, memória e Memória invertida), apresentado pelo professor em sala de aula, foram comprovados a partir do circuito montado em laboratório.

Bibliografia: Flip Flop RS e JK- Pagina da internet: http://escolaindustrial.com.br/escolaindustrial.com.br/Apostilas/M-1113a-1100-AlunoPor.pdf

Flip-Flops tem em seu circuito suas variáveis de entrada, uma entrada para o clock e duas saídas, normalmente denominadas com Q e Q’. Quando falamos de clocks e circuitos seqüências, temos que entender apenas um conceito muito simples, que as saídas se alteram de acordo com a entrada apenas quando damos um pulso no clock. Como você já pode notar os Flip-Flops são circuitos seqüências lógicos desenvolvidos para inúmeras aplicações, como por exemplo o controle de alguma produção industrial, onde temos varias entradas que devem funcionar de acordo com um determinada lógica para que a produção possa ser otimizada e nunca parar. Com isso em mente, podemos ver os tipos de Flip-Flops Flip-flop S-R Sincrono

Consiste no tipo mais básico de Flip-Flop, onde temos as duas saídas Q e Q’ e suas variáveis de entrada são um Set e um Reset, onde o Set seleciona o nível lógico 1 na saída do circuito (Q) e o Reset que seleciona o nível lógico 0 na saída (Q’). Abaixo temos seu circuito equivalente. Adote Q como a entrada atual do circuito RS Básico.

Tipo RS com Entrada Clock

Partindo da mesma lógica do tipo de Flip-Flop RS Básico, a única alteração em sua composição é a entrada de um clock, que é a peça fundamental para o circuito, pois quando ativo ele altera a saída de acordo com as variáveis de entrada. Abaixo segue o circuito equivalente.

Flip-flop J-K

O flip-flop J-K aprimora o funcionamento do flip-flop R-S interpretando a condição S = R = 1 como um comando de inversão. Especificamente, a combinação J = 1, K = 0 é um comando para ativar (set) a saída do flip-flop; a combinação J = 0, K = 1 é um comando para desativar (reset) a saída do flipflop; e a combinação J = K = 1 é um comando para inverter o flip-flop, trocando o sinal de saída pelo seu complemento. Fazendo J = K o flip-flop J-K se torna um flip-flop T.

Operação do Flip Flop JK

Tabela Verdade

J

K

Qpróx

Comentário

0

0

Qanterior

mantém

0

1

0

reset

1

0

1

set

1

1

Qanterior

alterna

1º Experiência: Objetivo: Entender o funcionamento do Flip-flop R-S.

Materiais:

Protoboard; Jogo de chaves; Multímetro; CI 7400; 2 leds vermelhos; Fios; Cabos banana; Ponta de prova; Fonte MPL-3303M

Procedimento: Montamos o circuito de acordo com a apostila do laboratório de eletrônica. Após o circuito montado realizamos os testes propostos na mesma apostila, e obtivemos os seguintes resultados .

Resultados: CLK

S

R

Qn+1

Qn+1’

0

X

X

Qn

Qnbarrado

Memória

1

0

0

Qn

Qnbarrado

Memória

1

0

1

0

1

Reset

1

1

0

1

0

Set

1

1

1

1

1

Indeterminado

Tabela1: Resultado do funcionamento do do circuito Flip-flop R-S

Figura 1: Montagem do circuito

Conclusão: Concluímos através deste experimento que os estados do flip flop( set, reset, memória e indeterminado), apresentado pelo professor em sala de aula, foram comprovados a partir do circuito montado em laboratório, onde, por exemplo, todos os estados SET e RESET estiverem em zero e o clock desabilitado o estado Qn+1 permanecera igual a Qn, isto foi observado através dos led´s do circuito.

2º Experiência: Objetivo: Entender o funcionamento do Flip-Flop JK.

Materiais:

Jogo de chaves; Jogo de botões; Multímetro;

Pontas de prova; 2 leds; Cabos banana; CI 7473; Protoboard; Fios; Fonte MPL- 3303M.

Procedimento: Montamos o circuito JK de acordo com a apostila fornecida em laboratório, verificando a pinagem do CI para efetuar as ligações, após a montagem obtivemos os resultados demonstrados abaixo.

Resultados: CL K 0

J

K

Q

Qbarrado

Estado

-----

------

Q0

Memória

1

0

0

Q0

1 1 1

0 1 1

1 0 1

0 1 Q0barrad o

Q0barrad o Q0barrad o 1 0 Q

Tabela 2: Resultado do funcionamento do Flip-flop JK

Figura 3: Circuito montado do flip-flop JK com o CLK em 1.

Memória Reset Set Mem. Invertida

Diagrama de tempos do flip-flop J-K

Conclusão: Concluímos através deste experimento que os estados do flip flop( set, reset, memória e Memória invertida), apresentado pelo professor em sala de aula, foram comprovados a partir do circuito montado em laboratório.

Bibliografia: Flip Flop RS e JK- Pagina da internet: http://escolaindustrial.com.br/escolaindustrial.com.br/Apostilas/M-1113a-1100-AlunoPor.pdf